本科毕设一晃就已然过去两个多月了,再过上一个多星期就要正式开始研究生的生活了,在此之前把本科毕设做个总结,算是对自己的知识框架再打包压缩罢,又算作是对后来者研究使用RapidIO技术的一个指引。嗯,一举两得,何乐而不为?

毕设是在去年12月份开始选题,那时倒也挺贪心,一心想做一个软硬结合的课题,最先开始选的课题现在都差不多忘光了,只记得选了之后将指导老师的姓名用站内搜索在好网上搜了下。这一看不知道,二看吓一跳呀!鸡皮疙瘩都快出来了。立马到教务处上删掉了,万幸那个指导老师没及时确认,由此逃过一劫… 再找了下其他的软硬结合的课题,看来看去感觉RapidIO还不错,对自己来说是全新的领域。RapidIO相关的课题共有两个,一个是B档难度的,只需在FPGA上实现,而另一个老师的是A档难度,需要使用串行RapidIO协议在DSP和FPGA之间完成通信。当时选题的时候还是患了老毛病,求新求刺激!RapidIO DSP FPGA这三者当时没有一个是很熟悉的,真是初生牛犊不怕虎!

选题之后自然是没法马上开工,毕竟还有1月份的考研初试咧。就这样拖到了来年的1月考完初试才开始了解这个课题——基于TMS320C6455的串行RapidIO技术及其实现。到Google Scholar上搜了下,发现包含TMS320C6455 和RapidIO两个关键词的论文还真不多,随便看了几篇,结果自然是云里雾里0.o 过年在家论文方面几乎也没什么动静,等到开学回学校也差不多要复试了,于是乎又拖了两个月才正式开始——也就是从4月3号左右开始全心准备毕设的。

毕设之前期准备

现在看来在前期最好先大概了解下课题,并进一步分解为小课题。这个可以让指导老师和师兄给个引导,一般在毕设的任务书和工作计划书中有详细说明,每条任务都可以认为是一个小课题,也许还要进一步细分。自己在这方面开始也没有经验,首先瞎摸索了一个星期也没啥收获,到实验室请教老师和师兄时才发现任务书和工作计划的好处。接下来就是根据任务书和工作计划自己拟定小课题和研究计划了。根据自己对课题的了解,我大概把毕设分为了如下几大块:

- 串行RapidIO协议的了解

- TMS320C6455芯片的编程使用

- TMS320C6455中有关串行RapidIO部分的初始化及使用

- Altera FPGA的烧写使用

- Altera FPGA中串行RapidIO IP核的了解和使用

- FPGA 和 DSP 进行串行RapidIO传输测试

- 论文写作——学习使用LaTeX对论文进行排版

可以看出要在短短的两个月里全部完成难度还是稍微有点大的,更坑爹的是后期实验室包含Altera FPGA的板子一直没画出来,于是乎便换到实验室现有的Xilinx平台,关键时刻还是得自己看着形势走呀,说多了都是泪…

毕设之论文思路

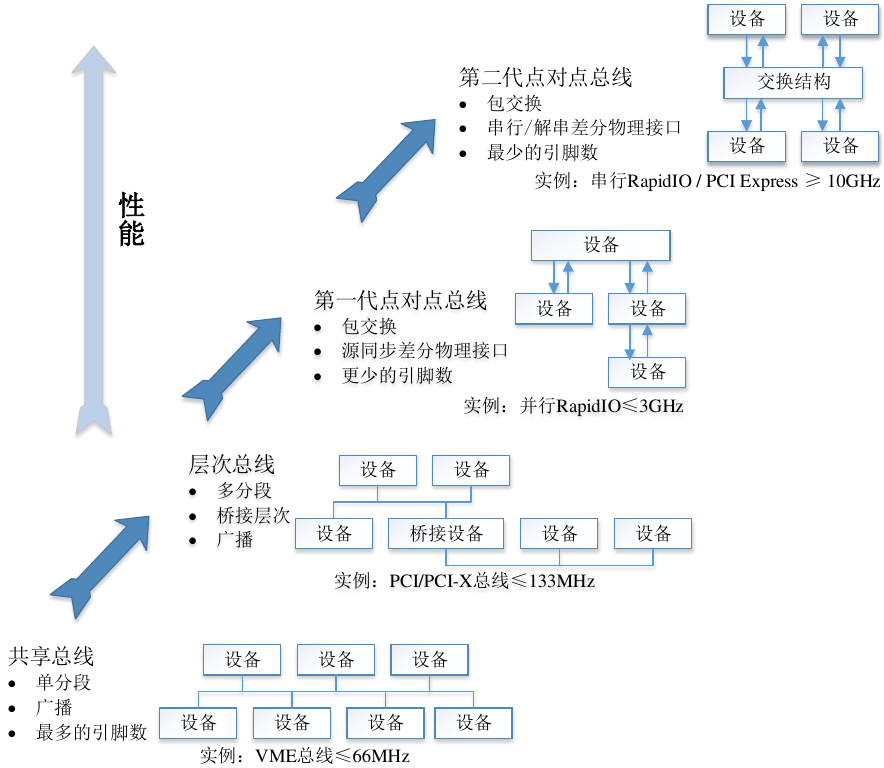

这个主体部分其实是参考了些硕士博士论文来的,当然也参考了RapidIO协会力荐的《RapidIO嵌入式系统互连》。首先简单描述了传统总线技术的不足,树个靶子,接下来自然就引申出了新型总线所需要的一些技术特性,满足这些技术特性的往往不止一个协议,所以对这些新型总线技术又有一个横向的比较,给些数据+曲线图,来点说服力,说明串行RapidIO在嵌入式互连领域的优势,接下来就是对RapidIO的大写特写了。写完RapidIO自然不是目的,毕竟论文标题中有个硕大的「实现」么。DSP和FPGA上的串行RapidIO实现自然也值得仔细地描述一番。OK,论文写到这差不多就快到尾声了,最后分析一下DSP和FPGA联调时使用串行RapidIO通信的一些实测数据画个图分析下原因差不多就完事了。KO! 大功告成。

最后的成果就是这么一篇论文咯——基于TMS320C6455的串行RapidIO技术及其实现.

从中抽出一张高清大图献上–>

何为串行RapidIO

串行RapidIO(serial RapidIO, 又简称SRIO)技术是一种高性能、低引脚数、点对点的基于数据包交换的系统级互连架构。其高带宽、低延时、高效率及高可靠性的优点为高性能的嵌入式系统内部互连通信提供了良好的解决方案。嗯,差不多就是这么一回事,我就不在这儿凑字数了,有兴趣的看我前边的论文就好了。

RapidIO架构规范了解

了解RapidIO最好的去处就是他们的官网了。

- 协议规范——加起来1000多页的样子,官网上是分开的,我把零碎的pdf合并在一起了,下载见我的Dropbox链接

- RapidIO : The Interconnect Architecture for High Performance Embedded Systems——RapidIO简明介绍,极具参考价值的一份文档。毕竟是技术白皮书嘛

- RapidIO嵌入式系统互连——可以说是了解RapidIO规范及在嵌入式系统中应用的必读读物,也是官网上推荐的唯一一本参考书目。同上,力荐

- RapidIO Technology Overview——可以瞅瞅,其实个人感觉文档RapidIO Technology Overview and Applications Presentation更有价值。

- Technology Comparisons——一系列(总线)技术的比较,PCI-e, Gigabyte-Ethernet

- RapidIO Wiki页面——权当作参考吧,其中提到的链接基本都在上边写过了

DSP和FPGA中RapidIO的使用

DSP和FPGA本身的使用及编程不必赘述,DSP使用C即可;FPGA嘛,verilog还是要方便些。找本书跟着敲敲代码烧点程序进去就差不多入门了。这方面我也算得上是半个门外汉,当时DSP入门用过的有手把手教你学DSP,了解下基本概念和实战操作用。FPGA之前选修课学得一知半解,等于没学,在做毕设的时候尝到自己种下的恶果了… 毕设时又翻了很多资料才算入了个门——同义词也就是过久了就差不多忘掉了。

DSP中RapidIO操作

个人感觉DSP中使用RapidIO还是比FPGA要简单些的,毕竟是过程性语句,好控制些。不像FPGA并行,而且有很多信号都有时序约束的。DSP中RapidIO的应用可以参考下串行 RapidIO: 高性能嵌入式互连技术,可以初步了解下RapidIO在DSP中的应用。更进一步的了解可以参考C64x的RapidIO视频部分——C64x+ 网络培训(九)——sRIO(串行RapidIO)

最重要的就是参考DSP芯片有关RapidIO部分的用户指南了,像C6455的Serial RapidIO User's Guide, 也是挺厚的一本,200多页来着,字都是很小的。

FPGA中的RapidIO操作

FPGA厂商一般都将RapidIO进行了封装,直接调用IP核即可,需要到Xilinx/Altera网站上申请评估版的IP,再自行设置些参数。否则有可能会在map或者translate时无法通过。当时自己在这一步偷了些懒,拿了实验板生成好的IP核直接用上了。本来准备对各个参数进行定制后做详细测评的,后来时间实在是太紧了就罢了(需要先申请评估版IP)。同DSP中的RapidIO用户手册,FPGA部分也有相应的IP核文档,500来页(Xilinx)…. 字同样也挺小,够看的了。

DSP和FPGA部分的测试代码在我的Github中,有需要的可以前往Serial RapidIO test with SEEDHPS6455自取,DSP部分的代码用srio_a_fixed目录内的就好。

期刊论文等资料

做学术研究,参考前人的成果是必不可少的啦,以下提供pdf和caj(知网专用的格式,少量硕博士论文)两种格式的论文和资料。所有资料都放在Dropbox里头了,需要的自取,尽量通过「Add to my Dropbox」同步下载,不然有可能因为流量耗费过多造成这些公开链接被暂时禁掉。slides目录下有我的答辩幻灯片,本来是想用beamer来做的,但是自己的图太多,还是用WPS省心些,字体主要使用文泉驿雅黑,如果觉得样式还不错的可以随便用,我的也是在秋叶PPT的答辩模板基础上稍微改动了下。封面大概就是下面这样子啦–>:

end

做毕设的两个多月的时间里,中间有一个月左右是早出晚归的,早上7点多坐着校车去,晚上5点的校车回,车费差不多花了¥150,心痛… 没有保送本校的不能报销=_= 好在最后把其中一组频率的速率给详细地测出来了,结果自然是和理论值有一定差距。DSP nwrite能稍微好点,接近理论值的90%,已经很不错了。

费了很大功夫整理了这么些东西,希望能对后头搞RapidIO的有点参考作用吧,也不枉我码这么多字了。如果Dropbox里边的东西对你有些帮助,请你一定一定要记得猛击我的Dropbox推广链接 哦~ 大家的空间都涨500M,何乐而不为?同步下来也方便,告别没完没了的备份,没有理由不用是不?

我敲一敲Enter,给海量的互联网空间里又代谢了10000+ bytes的数据……